Esquema de control del motor - IR2104S

Este esquema de control del motor se basa en el chip controlador de puente medio IR2104S y el transistor N-MOS AP30H80K, y utiliza el regulador externo XL2009E1 para suministrar energía al IR2104S.

Repositorio del proyecto: Collection_of_Motor_Driver_Design/DC_Motor/IR2104S

Vista previa en línea del proyecto:

Parámetros básicos

- Entrada

- VM: Fuente de alimentación para el motor, con una entrada de 12-36V (determinada por los parámetros de XL2009E1, IR2104S y AP30H80K).

- VCC_3V3: Voltaje de trabajo del sistema de puente H, con una entrada de 3.3-5V (determinada por los parámetros del chip lógico SN74LVC1G08DCKR).

- IN1/IN2: Entrada lógica externa, se recomienda que el voltaje de nivel alto y bajo siga a VCC_3V3, ver tabla de verdad a continuación.

- PWM: Entrada de PWM, el voltaje de nivel alto y bajo debe ser consistente con el voltaje de IN1/IN2.

- SD: Por defecto, es una entrada interna con resistencia de pull-down, es activa en nivel bajo (apaga el chip de puente medio IR2104S), se activa con una entrada externa en nivel alto (voltaje de VCC_3V3) para encender el IR2104S.

- Salida

- M+/M-: Conexión al motor externo.

- VCC_12V: Salida de regulación de voltaje del circuito integrado XL2009E1 en la placa, como una salida de alimentación de respaldo.

Cuando se utiliza el módulo de control del motor, el sistema de puente H debe compartir tierra con el controlador externo.

La tabla de verdad para el control lógico de este esquema es la siguiente:

| SD | IN1 | IN2 | PWM | Estado del motor |

|---|---|---|---|---|

| 0 | x | x | x | Deslizamiento |

| 1 | 1 | 0 | 1 | Rotación en sentido horario |

| 1 | 0 | 1 | 1 | Rotación en sentido antihorario |

| 1 | 1 | 1 | x | Freno |

| 1 | 0 | 0 | x | Freno |

| 1 | x | x | 0 | Freno |

Principios básicos

Circuito lógico

Para controlar un motor, se necesitan dos pares de circuitos de puente medio para formar un puente H completo. Para controlar el estado del motor según la tabla de verdad, se utilizan dos circuitos de compuerta AND para realizar una operación AND entre la señal de entrada PWM y las señales IN1/IN2, y se envía el resultado (PWMA/PWMB) a la entrada IN del IR2104. La entrada de alimentación del chip lógico está conectada en paralelo con un condensador de desacoplamiento de 100nF.

Circuito de regulación de voltaje

El circuito de regulación de voltaje se basa en el chip Buck XL2009E1, que convierte la fuente de alimentación externa en un voltaje estable de 12V para alimentar el chip IR2104S (cuyo rango de voltaje de alimentación es de 10-20V).

Para obtener más información sobre el diseño del módulo de regulación, consulte el artículo Esquema de alimentación (Buck) - XL2009E1 (en inglés).

Circuito de control del puente medio

Para obtener más información sobre los conceptos básicos del control del motor, consulte el artículo Diseño del controlador de motor de corriente continua (en inglés).

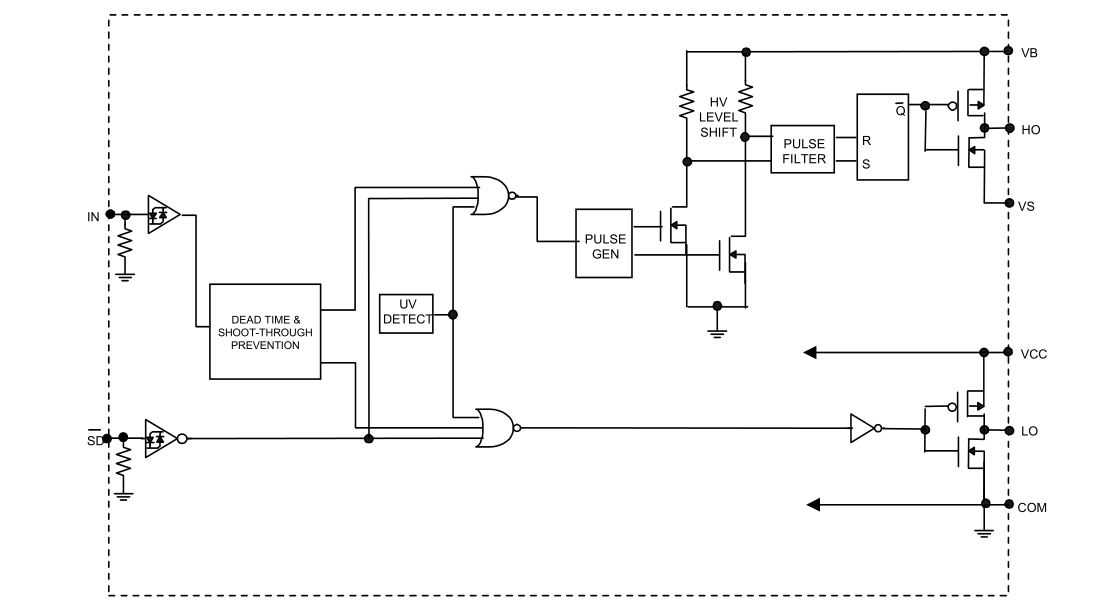

IR2104S es un chip controlador de puente medio de Infineon. Sus principales características son las siguientes:

- Tensión de resistencia de flotación de hasta +600V.

- Tensión de alimentación de la compuerta de 10-20V.

- Niveles de entrada lógica compatibles con 3.3V/5V/15V.

- Otras características:

- Bloqueo por baja tensión.

- Control integrado del tiempo de retardo.

- Lógica de prevención de conducción cruzada.

- Fase en el mismo sentido que la entrada lógica.

- Ambos transistores se apagan cuando se desactiva.

- Retardo de propagación coincidente entre los transistores superior e inferior.

Diagrama interno:

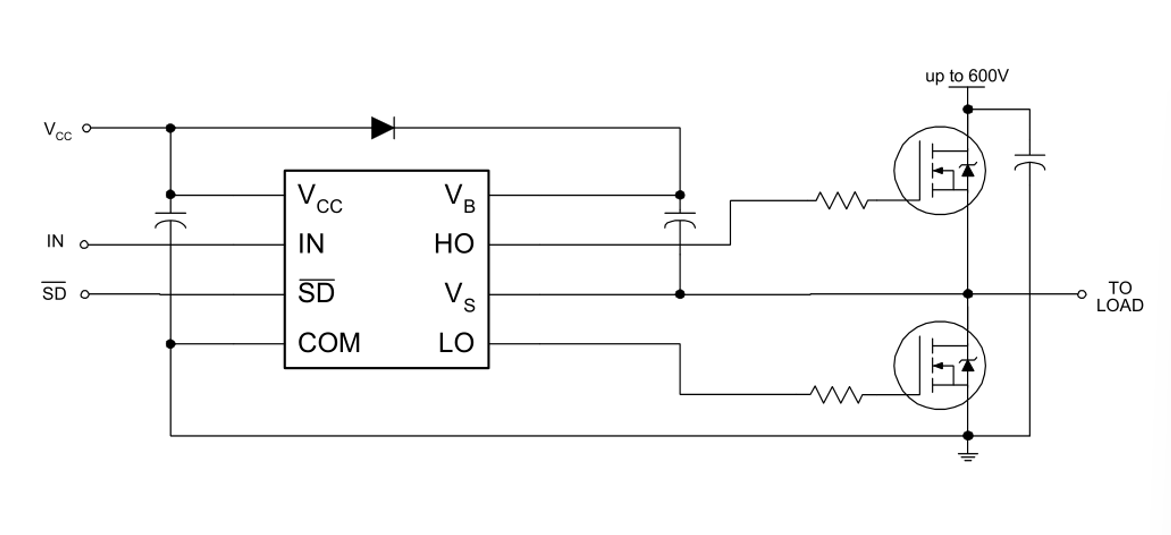

Esquema de aplicación típico:

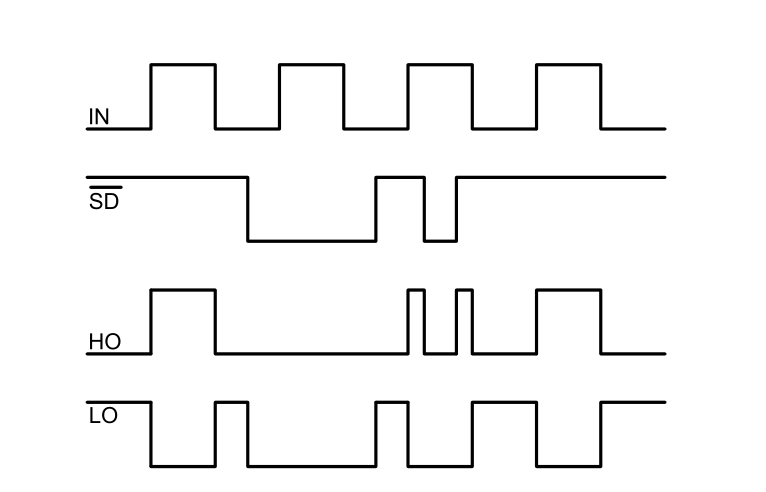

En este diseño, el IR2104S se alimenta con 12V y se conecta en paralelo con un condensador de desacoplamiento de 100nF. IN es el pin de entrada lógica, se considera alto cuando la tensión de entrada es superior a 3V y bajo cuando es inferior a 0.8V. La señal de nivel alto y bajo de las salidas PWMA/PWMB, generadas por la operación de la lógica, controla la activación y desactivación de los transistores superior e inferior. SD es la entrada de desactivación externa (activo en bajo). IN y SD se mezclan como entradas, y el siguiente diagrama muestra el estado secuencial de los pines de la compuerta HO/LO correspondientes a los transistores superior e inferior:

Como se puede ver, si la entrada IN es alta, la compuerta del transistor superior se activa en alto y la del transistor inferior se desactiva en bajo, y viceversa. Si SD detecta un nivel bajo, tanto si la entrada IN es alta como baja, ambos transistores se desactivarán.

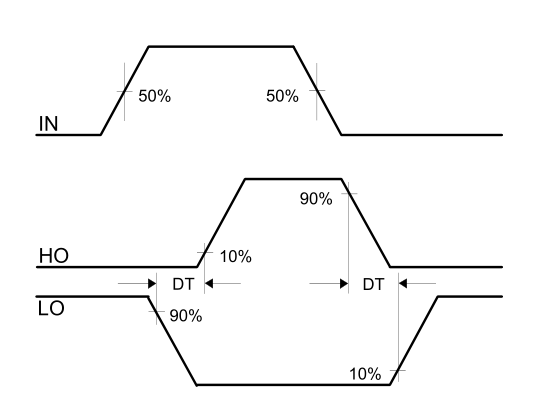

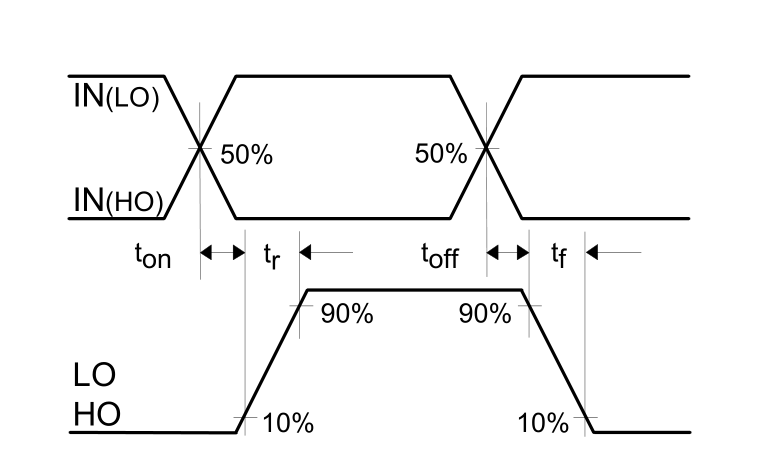

Para evitar la conducción simultánea de los transistores superior e inferior en el mismo puente (shoot-through), el IR2104S integra un control de tiempo de retardo. El siguiente diagrama muestra el tiempo secuencial de control del tiempo de retardo:

Donde el valor típico de DT es de 520ns.

El siguiente diagrama muestra el tiempo secuencial de activación/desactivación de los transistores superior e inferior:

Donde el valor típico de \(t_{on}\) es de 680ns y el valor típico de \(t_{off}\) es de 150ns.

Debido a que se utilizan transistores N-MOS en este diseño (la condición de conducción es \(V_g-V_s>V_{gs(th)}\)), se requiere un circuito de flotación de alta tensión en el lado alto para activar correctamente el transistor superior. Este diseño utiliza un condensador cerámico MLCC de 1uF/50V conectado entre los pines VM y VB, lo que hace que el voltaje de nivel alto en el pin HO sea mayor que \(V_{GS(th)}\) del N-MOS, es decir, la tensión de alimentación del IR2104S menos la caída de tensión directa del diodo, lo que permite que el transistor superior conduzca correctamente.

La selección de los transistores MOS debe tener en cuenta los parámetros \(V_{DSS}\), \(V_{gs(th)}\), \(I_D\) y \(R_{DS(on)}\). La determinación de \(V_{DSS}\) se basa en la tensión del motor de accionamiento más un margen suficiente; \(I_D\) se determina en función de los requisitos de la aplicación más un margen suficiente; y cuanto menor sea \(R_{DS(on)}\), mejor. Teniendo en cuenta estos parámetros y el precio, este diseño utiliza el AP30H80K.

Para el modo de atenuación, dado que el IR2104S no tiene atenuación síncrona integrada, se utiliza un diodo Schottky SS34 para la atenuación asíncrona.

Referencias y agradecimientos

- Explicación detallada del circuito de control de motor H-bridge STM32+IR2104S

- Dudas sobre el circuito de capacitancia de flotación en el controlador de puente H con MOSFET

- AN-6076: Guía de diseño y aplicación de circuitos de capacitancia de flotación para ICs de control de alta tensión de la compuerta

- ¿Por qué el PWM no puede ser demasiado rápido para controlar un motor? ¿Por qué el PWM complementario para controlar los MOSFETs superiores e inferiores no puede tener un ciclo de trabajo del 100%?

Dirección original del artículo: https://wiki-power.com/

Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.